De: "Guilhem Emmanuel (ALTRAN)" <emmanuel.guilhem.external@cnes.fr> Objet: Antenna 3 failure HF pre-amplifier latch up hypothesis Date: 2 avril 2024 à 11:18:36 UTC+2 À: Walter Puccio <wp@irfu.se>, Xavier Bonnin <Xavier.Bonnin@obspm.fr>, "roc sci-ops" <roc.sciops@sympa.obspm.fr>, Anders Eriksson <Anders.Eriksson@irfu.se>, Niklas Edberg <ne@irfu.se>, Dekkali Moustapha <moustapha.dekkali@obspm.fr>, Anik De Groof <Anik.DeGroof@esa.int>, Christopher Watson <Christopher.J.Watson@esa.int>, Pedro Osuna Alcalaya <Pedro.Osuna@esa.int>, "antonio.vecchio@obspm.fr" <antonio.vecchio@obspm.fr>, "milan.maksimovic@obspm.fr" <milan.maksimovic@obspm.fr>, Raulin Desi <Desi.Raulin@cnes.fr>, Lorfevre Eric <Eric.Lorfevre@cnes.fr> Cc: "Fossecave Herve (ALTRAN)" <Herve.Fossecave.external@cnes.fr>, "Sinibaldi Clement" <Clement.Sinibaldi@cnes.fr>

Dear All,

You can find in this email a summary of the Antenna 3 failure : the HF preamplifier hypothesis.

During the ANT3 failure a "shortcut" between the antenna and the GND has been seen through BIAS measurements and PA HF preamplifier measurements.

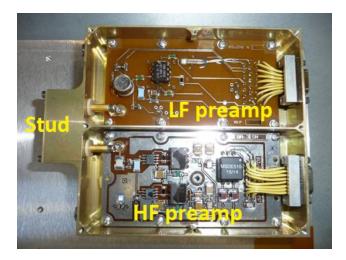

The HF preamplifier is located next to LF preamplifier in the same box, linked to the antenna via a stud.

## Evaluation of the shortcut resistance:

- BIAS data analysis

According to BIAS Specification (RPW-SYS-MEB-BIA-SPC-00001-IRF\_Iss01\_Rev06) The BIAS current can be set in the following range:

$\,\circ\,$  Bias current range -100mA to 100mA In 16384 steps

During the anomaly the maximum voltage of the sweep is 20V

corresponding to  $100\mu$ A witch leads to a plasma resistance of 200kOhm.

$_{\odot}\,$  On the anomaly the BIAS sweep resolution is 38 steps, it is equivalent to a 5.kOhm minimum resolution.

• We can only assess that the shortcut resistance is lower than 5kOhm.

- HF preamplifier data analysis

According Walter Pucio email (2/2/2024) the resistance was evaluated to 25Ohms, but he took the assumption of an antenna base capacitance around 25e-6pF.

The measurement done on QM antenna shoes a base capacitance of SOLO-SY-TN-271-CNES of 75pF including FET capa (25pF).

Thanks (very much) to Walter formula we can evaluate the resistance of 60Ohm instead of 25Ohms.

This analysis shows that what we call a short cut can be a resistance of an order of magnitude close to the HF preamplifier input resistances (1500hm).

# **Evaluation of the shortcut potential difference**

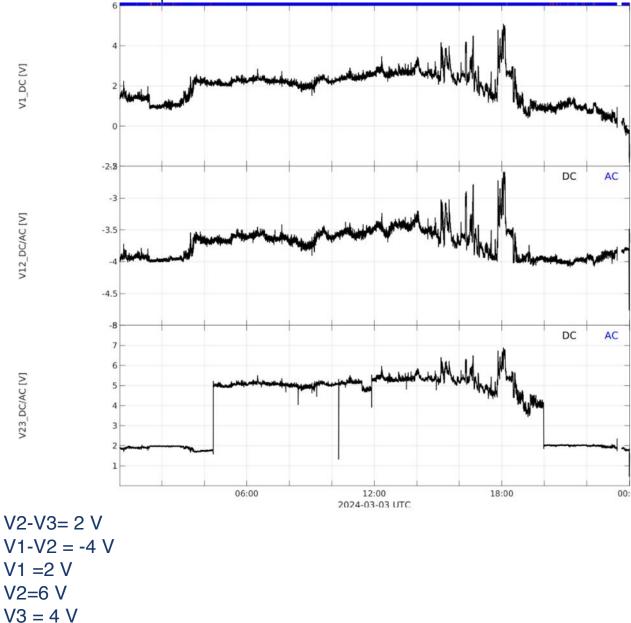

According to LFR F3 measurement during the anomaly we can determine the DC potential in Antenna 3:

So the shortcut potential value is close to 4V.

## Historic latch-up

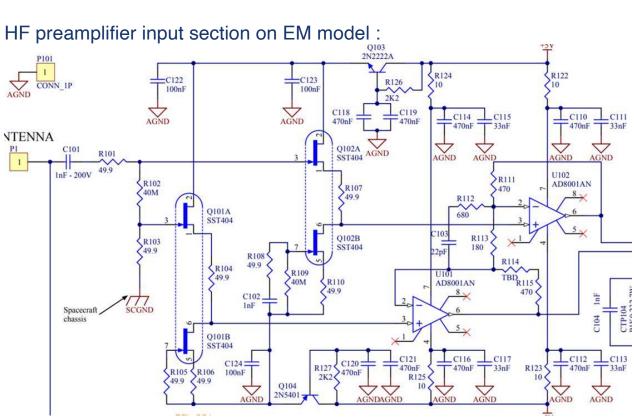

During RPW integration a latch-up of HF preamplifier has been see on EM model, during the BIAS sweeps. The transistors or JFET Amplifier in the HF preamplifier front end turns to short cut while a high voltage was applied by BIAS during the sweeps. The electronic architecture was not identical :

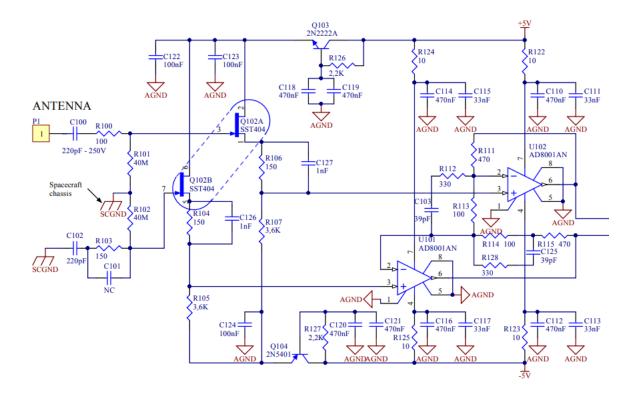

Due to this unexpected latchs up the input section was simplied, but some transistors remains:

With this modification, on ground, the input transistors never latch-up again.

## Application to flight anomaly:

Status:

$\cdot$  The anomaly occurs during BIAS sweeps when a high voltage transient is applied at HF preamplifier input (~30V).

$\cdot$  During flight the resistance of the short cut during the anomaly is around 600hm and the potential is around 4V.

Hypothesis

• The transistor ST404 and the JFET AD 8001 are used out of the max ratings:

o ST404 : 40V

#### ABSOLUTE MAXIMUM RATINGS

| Gate-Drain, Gate-Source    | Voltage                          | -40 V |

|----------------------------|----------------------------------|-------|

| Gate Current               |                                  | 10 mA |

| Lead Temperature (1/16" fr | rom case for 10 sec.)            | 300°C |

| Storage Temperature :      | U Prefix65 to<br>SST Prefix55 to |       |

|                            |                                  |       |

For applications information see AN106.

Document Number: 70247 S-04031-Rev. F, 04-Jun-01

### • AD8001 : 1,2V

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltage 12.6 V                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Power Dissipation @ 25°C <sup>2</sup>                                                                                                                      |

| PDIP Package (N)1.3 W                                                                                                                                               |

| SOIC (R)                                                                                                                                                            |

| 8-Lead CERDIP1.1 W                                                                                                                                                  |

| SOT-23-5 Package (RT)0.5 W                                                                                                                                          |

| Input Voltage (Common Mode) $\dots \dots \dots$                     |

| Differential Input Voltage ±1.2 V                                                                                                                                   |

| Output Short Circuit Duration                                                                                                                                       |

| Observe Power Derating Curves                                                                                                                                       |

| Storage Temperature Range N, R65°C to +125°C                                                                                                                        |

| Operating Temperature Range (A Grade)40°C to +85°C                                                                                                                  |

| Lead Temperature Range (Soldering 10 sec) 300°C                                                                                                                     |

| NOTES                                                                                                                                                               |

| Stresses above those listed under Absolute Maximum Ratings may cause perma-<br>nent damage to the device. This is a stress rating only; functional operation of the |

| <b>Operating Junction Tem</b> | perature55 to 150°C          |

|-------------------------------|------------------------------|

| Power Dissipation :           | Per Side <sup>a</sup> 300 mW |

|                               | Total <sup>b</sup> 500 mW    |

| Notes                         |                              |

a. Derate 2.4 mW/°C above 25°C

b. Derate 4 mW/°C above 25°C

www.vishay.com 8-1

#### MAXIMUM POWER DISSIPATION

The maximum power that can be safely dissipated by the AD8001 is limited by the associated rise in junction temperature. The maximum safe junction temperature for plastic encapsulated devices is determined by the glass transition temperature of the plastic, approximately 150°C. Exceeding this limit temporarily may cause a shift in parametric performance due to a change in the stresses exerted on the die by the package. Exceeding a junction temperature of 175°C for an extended period can result in device failure.

While the AD8001 is internally short circuit protected, this may not be sufficient to guarantee that the maximum junction temperature (150°C) is not exceeded under all conditions. To ensure proper operation, it is necessary to observe the maximum power derating curves.

A repeated stress, like a SWEEP BIA,S every week can produce a damage at the AD8001 input. But the AD8001 input is protected by Diodes.

One hypothesis is : the AOP is saturated, and stays block in saturation as long as a reset is applied.

When the AD8001 is saturated a high current is driven in the +5V power line, And be set to 3,1V the maximum output swing of the preamplifier, This is more or less the voltage seen by the LF preamplifier (-4V calculated previously).

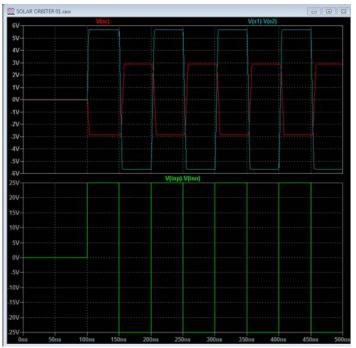

Simulations on HF preamplifier (Done by H. Fossecave)

• A pluse of 25V is applied to AOP input (green curve)

$\,\circ\,$  A saturation is seen at one preamplifier input (red curve), the

differential curves are also saturation (blue curve) :

At the end of the pulse the preamplifier returns to nominal mode, so the remaining saturation seen during the anomaly could be due to a stress of some components.

## perspectives:

All the HF preamplifiers are submitted to a Voltage differential on inputs above maximum ratings during BIAS sweeps. This bad use as not been identified during RPW development periods.

The urgent action to be taken is to stop right now the BIAS sweeps as long as a solution has been implemented.

Identified solutions :

- Easy to be set : Do the sweeps while the HF preamplifier is OFF

- More tricky : Update sweep table in order to moderate the amplitude of the sweeps. A command exists : TC\_DPU\_LOAD\_BIAS\_SWEEP. This command is a DAS command and not a BIAS setting, so the way to upload a new command is cooperation between LESIA operation team and IRFU Team. The SW description describes precisely the commands to be set : RPW-SYS-SSS-00013-LES

Best regards,

Emmanuel Guilhem with the help of Hervé Fossecave.

Emmanuel Guilhem (CAP GEMINI) X-IFUTéléphone portable pro: (+ 00 33) 6 08 70 33 18 Bureau : (+ 00 33) 5 61 28 76 04 E-mail : emmanuel.guilhem.external@cnes.fr